## Mansoura Engineering Journal

Volume 30 | Issue 1

Article 3

12-16-2020

# Programmable Protection of Industrial Lead Acid Battery Supplied by Solar Cells Array.

Saad Saad Eskander Electrical Engineering Department, Faculty of Engineering, Mansoura University, Egypt

Follow this and additional works at: https://mej.researchcommons.org/home

#### **Recommended Citation**

Eskander, Saad Saad (2020) "Programmable Protection of Industrial Lead Acid Battery Supplied by Solar Cells Array.," *Mansoura Engineering Journal*: Vol. 30 : Iss. 1, Article 3. Available at: https://doi.org/10.21608/bfemu.2020.130303

This Original Study is brought to you for free and open access by Mansoura Engineering Journal. It has been accepted for inclusion in Mansoura Engineering Journal by an authorized editor of Mansoura Engineering Journal. For more information, please contact mej@mans.edu.eg.

### PROGRAMMABLE PROTECTION OF INDUSTRIAL LEAD ACID BATTERY SUPPLIED BY SOLAR CELLS ARRAY

### الحماية المبرمجه لبطارية رصاص حامضية صناعيه تغذى بمنظومة خلايا شمسية

S. S. Eskander

Assistant Professor, Electrical Engineering Department, Faculty of Engineering, Mansoura University, EGYPT

فى هذا البحث يتم تصميم نظام حماية مبرمج مناسب لبطارية رصاص حامضية موصلة بمنظومة خلايا فوتوفولتية. ويعتبر المتحكم الدقيق الموجود فى نظام الحماية المقترح هو عقل هذا النظام. ولقد تم تصميم هذا النظام بناء على قياسات لقيم معينة لجهد البطارية. هذة القيم يتم تحديدها عمليا عند قياس الاداء الكهربى للبطارية المراد حمايتها. ويحتوى نظام الحماية المقترح تصميمه على ثلاثة مقارنات وسنة دو اندر لتر انزستورات فى وضع غلق ابتدائى ومتحكم دقيق ومرحلة للخرج تحتوى على دائرتى تر انزستور ومتمين. وقد تم اقتراح خطة تم برمجتها للتشغيل المبرمج لنظام الحماية من اجل للخرج تحتوى على دائرتى عمليتى الشحن و التفريخ. وقد اوضح البحث التطابق بين خطة التشغيل المعترحة و التشغيل الفعلى للنظام العماية من الجهد حقيقة يوضح خطة التشغيل المبرمجة.

#### Abstract

Proposed protection system based on programmable intelligent microcontroller (PIC) suitable for lead acid battery connected to solar cells array is designed and operated. The PIC represents the brain of the designed protection system. The system design is based upon measured parameters known as battery voltage set points. These points are determined by measuring experimentally the electrical behavior of the battery to be protected. The proposed protection system composes of three comparators, six normally off transistor circuits, PIC chip, and the output stage which contains two transistor circuits as well as two relays. Proposed strategy for the operation of the protection system is carried out to protect the battery against overcharge and over discharge. The paper presents the accurate operation of the system according to the proposed operating strategy. It presents also the proposed truth table which defines the PIC operation.

#### Introduction

Electrical storage batteries can be divided into two major categories, primary and secondary batteries [1]. Primary batteries can store and deliver electrical energy, but can not be recharged. These types of batteries are not used in photovoltaic (PV) systems because they cannot be recharged. Secondary batteries can store and deliver electrical energy, and also be recharged by passing a current through it in an opposite direction to the discharge current. Common lead acid batteries used in cars and PV systems are secondary batteries. The energy storage capability of the lead acid battery varies with battery design and use, and in all cases, the practical discharge capability is at best only 60%-70% of the theoretical capability [2]. Battery manufacturers often refer to three modes of battery charging, normal or bulk charge, finishing or float charge and equalizing charge [3]. Bulk or normal charging is the initial portion of a

Accepted March 31, 2005.

charging cycle, preformed at any charge rate which does not cause the cell voltage to exceed the gassing voltage. Bulk charging generally occurs up to between 80 and 90% state of charge. Once a battery is nearly fully charged, voltage and/or current regulation are generally required to limit the amount of the energy supplied to the battery to prevent Finish charging is usually overcharge. conducted at low or medium charge rate. An equalizing charge generally occurs with a current limited chargers with higher voltage limits than set for the finishing or float charge. To limit gassing and electrolyte loss to acceptable levels, proper selection of the charge controller voltage set point is critical in PV system. If too low of regulation voltage is used, the battery will be under charge (not full charge). If too high of a regulation voltage is used, the battery will be overcharged. Both undercharge and overcharging will result in premature battery failure and loss of load in stand-alone PV system [4].

# E. 10 S. S. Eskander and the stand of the stand sta

Charge controllers prevent excessive battery overcharge by interrupting or limiting the current flows from the array to the battery when the battery becomes fully charged. When a battery is excessively discharged repeatedly, loss of capacity and life will occur. To protect batteries from under discharge, most charge controllers include an optional feature to disconnect the system loads once the battery reaches a low voltage or low state of charge condition [5, 6]. The purpose of the charge controller is to supply power to the battery in a manner to fully recharge the battery without overcharging. Depending on the regulation algorithm, the current may be limited while maintaining the regulation voltage or remain disconnected

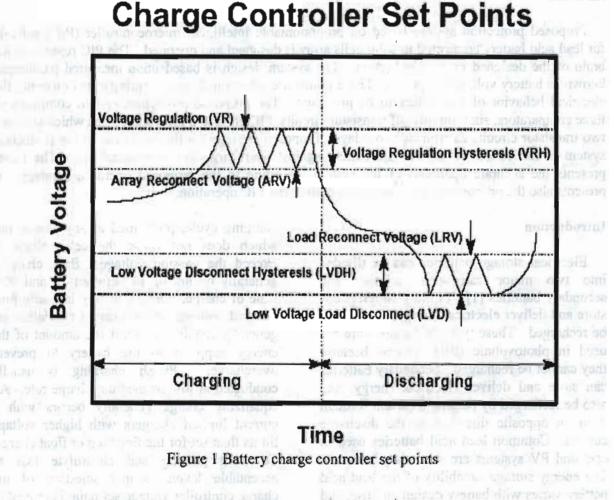

until the battery voltage drops to the array reconnect set point. While the specific regulation method or algorithm varies among charge controllers, all have basic parameters and characteristics [7]. The voltage regulation set points (VR) is one of the key specifications for charge controllers. The voltage regulation set point is defined as the maximum voltage that the charge controller allows the battery to reach, limiting the overcharge or discharge of the battery. This paper presents the design and operation of proposed intelligent charge-discharge controller of a lead acid battery according to specific voltage regulation set points shown in Fig.1.

etaentilister haven an ministration of the etainege conductor variege set paraminister et dat PV gream. It too hav of legitletion variage is more, the batt or will be under sharpe (not full campe). It is high of a regulation voltage is more the batter will be eventianged. Both uses the batter will be eventianged. Both understange and eventinging will regulate provisions for etaine and term tradies of provisions for the minister.

II. II. III.

#### **Battery Model**

The battery under control is charged from solar cells array to work as a charger. The relationship between its voltage and current during charging / discharging process is described by the following exponential mathematical model [8];

$I = I_{o} \{ \exp [\alpha F/ (RT) (E-E_{0})] - \exp [-(1-\alpha)/(R.T) F (E-E_{0})] \}$ (1)

#### Where;

$I_o$  is the exchange current density, I is the current density, E is the actual electrode potential,  $E_o$  is the open circuit electrode potential,  $\alpha$  is the transfer factor describing the efficiency of the over voltage on forward (charging) and backward (discharging) reactions,  $R_1$ , F and T have the usual meaning: gas constant, Faraday constant and temperature.

The battery open circuit voltage is a temperature dependent and can be calculated according to the following equation:

$$E_{0}(t) = E_{0}(2980T) + (dE_{0}/dT) iso (T-298+0.5(d^{2}E_{0}/dT^{2}) iso (T-298)^{2}$$

(2)

Where:

$(dE_0/dT)_{iso}$  is the isothermal temperature coefficient and T is the cell temperature in  $^{O}K$

#### Model of Photovoltaic Array

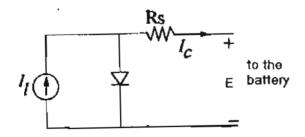

The PV cell exhibit non linear characteristic and can be modeled by the electric circuit shown in Fig. 2.

Figure 2 Circuit model of photovoltaic

$$E = -I_L R_S + (1 / A) \ln (1 + (I_L - I) / I_O)$$

(3)

Where  $I_{\downarrow}$  is the light current, I is load current, A is constant,  $I_0$  is dark current,  $R_S$  is series resistance of the array.

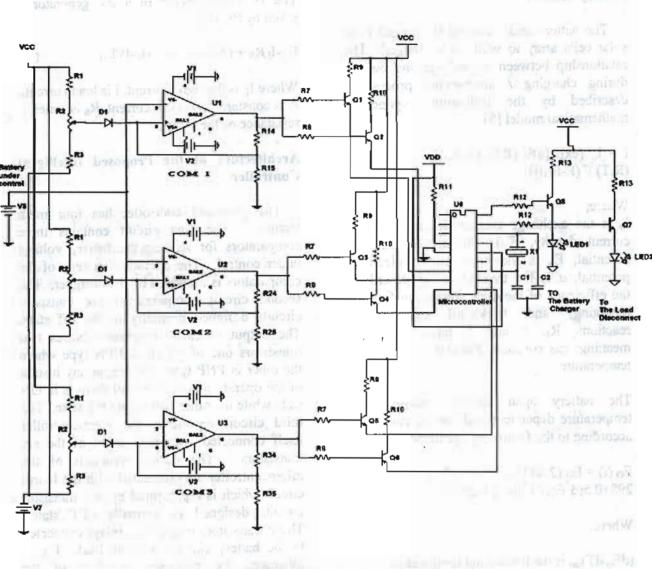

#### Architecture of the Proposed Intelligent Controller

The proposed controller has four main The first circuit contains three circuits. comparators for sensing the battery voltage under control. The operation strategy of the comparators is proposed by the designer. The second circuit composes of six transistor circuits designed normally in the off stats. The output of each comparator biases two transistors one of which is NPN type where the other is PNP type. Hence, at any instant of the operation period, one of them is in ON state while the other will be in OFF state. The third circuit represents the microcontroller itself connected with the output of the six transistors. The output terminals of the microcontroller are connected with the fourth circuit which is represented by two transistor circuits designed in normally OFF states. These transistors trigger two relays connected to the battery charger and the load. Fig. 3 illustrates the proposed topology of the intelligent battery charge-discharge controller.

and a market and

S. Amata

Figure 3 Topology of proposed intelligent battery charge controller

#### **Proposed Design of the Controller**

The design of the controller is initiated by selecting the voltage set points of the battery. These points are selected by the designer from the battery, under control, electrical behavior. battery behavior The is recorded experimentally. Each comparator of the proposed controller has two selected set These points refer to the upper points. trigger, UTP, and the lower trigger, LTP, points. The UTP of the comparator 1,  $U_1$ , is selected as the voltage regulation set point, V<sub>R</sub>, of the battery. For the lead acid battery, under test, it has a value of 14.4 V. On the other hand, the LTP of comparator 1 is

selected such that slightly lower than of U<sub>1</sub>. The selection of it depends upon the collection of the maximum value of solar energy incident upon the photovoltaic The upper trigger point of transducer. comparator 2 is selected such that it has a value lower than U<sub>1</sub> and greater than L<sub>1</sub>, it selected as 14.1 V for the tested battery. Conversely, the lower trigger point, L2, of the second comparator is selected slightly lower than  $L_1$ , it is 13.8V. Comparator 3 is designed to operate during very low insolation periods and during the periods of no insolation. This comparator operates to connect or reconnect the load. The upper trigger point of this comparator is selected

such that, it has a value greater than the battery voltage corresponding under charge value. Hence the value of  $U_3$  is selected as 12.7 V for the battery under test. This value

is known as the load reconnected voltage, LRV. The lower trigger voltage of comparator 3,  $L_3$ , is selected such that a value slightly greater than the under charge voltage of the battery. Consequently, this value is assumed as 11.7 V for the battery under test. As all values of the upper and lower trigger points of all comparators are determined, the design of each element of the comparator circuits is determined as follows;

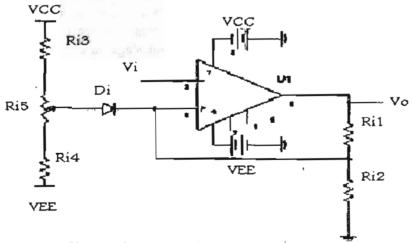

Fig. 4 represents the topology of each comparator circuit used in the proposed controller.

The design of each comparator has a similar proposed procedure below;

The output voltage of the *i*th comparator is equal to V<sub>cc</sub>-1, where V<sub>cc</sub> is the supply bias voltage. Since the resistor Ris is designed such that it has a voltage drop must be equal to U<sub>i</sub>, upper trigger level of the comparator. The current I<sub>2</sub> must be selected such that;

$I_2 >>> I_{bias}$ (4)

Where, Ibias is the value of bias current of the IC. This current is obtained from the IC data sheet. Hence:

$R_{i5} = U_i / I_{bias}$ (5) The proper design of the comparator circuit is such that, the lower trigger point must be adjusted between two levels Li min and Li max. For obtaining the minimum value of L, the adjustable point of resistor Ri2 must be connected directly to resistor Ri3. Hence; (6)

$I_1R_{i3} - V_{EE} - L_{i\min} - V_{Dif} = 0$

Where, V<sub>EE</sub> is the negative voltage value of the biasing supply and V<sub>Dif</sub> is the forward

voltage drop in the diode, thus, the design value of R<sub>in</sub> is;

$$R_{i3} = (V_{EE} + L_{i\min} + V_{Dif}) / I_1$$

(7)

$I_1$  is selected greater that  $I_2$

For obtaining the maximum value of the lower trigger point Limax input to the comparator, resistor Ri2 must be connected in series with Ri3. So;

$I_1 (R_{i3} + R_{i2}) - V_{EE} - L_{i \max} - V_{Dif} = 0$ (8)Hence; '

$R_{i2} = ((VEE + L_{i max} + V_{Dif}) - I_1R_{i3}) / I_1$ (9) R<sub>il</sub> is obtained from the following equation;

$V_{cc} + V_{EE} = I_1 (R_{i1} + R_{i2} + R_{i3})$ (10)Hence;

$R_{i1} = (V_{cc} + V_{EE} - I_1 (R_{i2} + R_{i3})) / I_1$ (11)The design value of  $R_{i4}$  is obtained as;

$$R_{14} = ((V_{cc} - 1) - U_i) / I_2$$

(12)

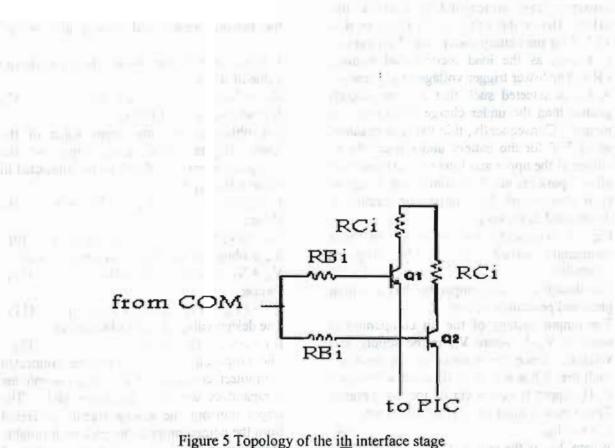

The proposed controller must be connected with interface stages. These stages couple the comparators with the intelligent pick. The stages transmit the analog signals generated from the comparators to the pick with suitable specifications related to the PIC. Fig. 4 illustrates the ith interface stage.

Figure 4 Topology of the ith comparator circuit

#### S. S. Eskander E. 14

2001. USBAN MARKEN AND A MARKEN AND A

The proposed controller has three similar stages each of which has the same design The design is initiated by procedure. obtaining the load and pick and specifications. These specifications are obtained from the pick data sheet. Hence, for each pin, the pick pin voltage and current is assumed as;

$V_L = 2 V$  and  $I_L = 2 mA$

Where;  $V_L$  and  $I_L$  are the voltage and current required for pick operation. Consequently, the values of R<sub>ci</sub> and R<sub>ci+1</sub> are identical and also R<sub>Bi</sub> and R<sub>Bi+1</sub>. So:

$R_{ci} = (V_{cc} - V_L) / I_L$ (13) $R_{ci+1} = R_{ci}$

From transistor data sheet, the amplification factor hFEmin is determined. Hence;  $I_{Bi} = I_{Bi+1} = L_L / h_{FEmin}$ (14)

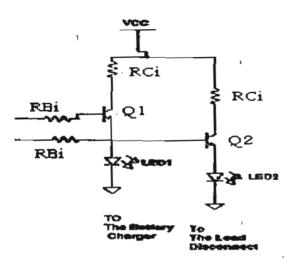

The output stage contains two transistors. The base of each transistor is triggered by the signal output of the pick. The emitters of the transistors are connected with the battery charger and the load through LEDS, to indicate the state action, and relays. The relays are used for connecting or reconnecting the battery charger and the load. The two output stages are similar and have the same design procedure. Fig. 6 represents one of the output stages.

Figure 6 Topology of ith output stage

The design values of  $R_c$  and  $R_B$  depend on the relay specifications which are obtained from data sheet. The operating current and voltage of the relay obtained from the data sheet may be acted as,  $I_R$  and  $V_R$ . Hence;  $R_c = (V_{cc} - V_R - V_{DF}) / I_R$  (15)

And from the transistor data sheet,  $h_{FEmin}$  is obtained. So,

$R_{B} = (V_{o} - V_{Beon} - V_{DF}) / I_{B}$ (16) Where V<sub>0</sub> is the amplitude of the pick output voltage and V<sub>BEon</sub> is taken as 0.7 V.

The pick bias circuit elements,  $R_{11}$ ,  $C_1$ ,  $C_2$  and X, are obtained from its data sheet.

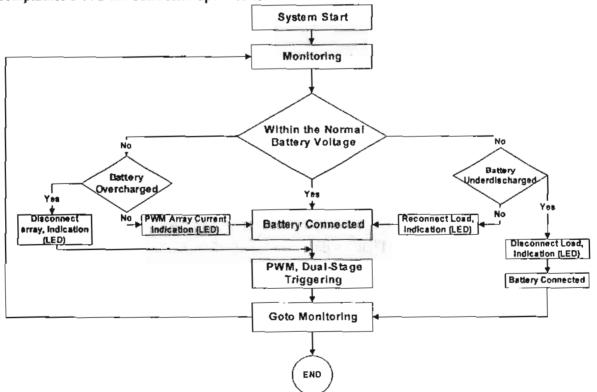

# Proposed Operation Strategy of the Charger

Initially the battery is fully charged and its voltage is greater than  $U_3$ . Hence, the output of comparator 3 becomes negative. On the other hand, the outputs of comparators 2 and 1 become positive. This means that, the load and the battery charger, solar cells array, are connected to the battery. Hence, the battery is in charge condition and its voltage goes up. As the battery voltage reaches to  $U_2$ , 14.1 V, comparator 2 changes its output state from positive to negative. If the battery voltage is continuously increasing to  $U_1$ , 14.4 V, comparator 1 changes its output state from positive to negative. During periods of low

and no insolation, the battery voltage slightly decreases from L<sub>1</sub>, 14 V, and comparator 1 is changed its output state from negative to At this moment the charger is positive. reconnected again to the battery. As the battery voltage is continuously decreasing till L<sub>2</sub>, 13.8 V, comparator 2 changes its output state from negative to positive. The action of comparator 2 is to connect the whole current of the array to the battery. As continuously decreasing of the battery voltage till L<sub>3</sub>, 11.7 V, comparator 3 changes its state from positive to negative to disconnect the load from the battery.

#### **Intelligent Data Input of the PIC**

The output of each comparator is converted into two signals, by the interface stages, one of which is in high form represented by 1 where, the other signal becomes in a low form represented by 0. Consequently a binary word is obtained from the whole stages of the interface. This word refers to the input to the PIC pins. The input binary word input to the PIC pins. The input binary word input to the PIC changes according to the battery voltage set points. The following table represents the PIC input in binary form and the determined output action required from the PIC.

# E. 16

S. S. Eskander

Table 1 the truth table for the outputs of interface stages and the output action of the PIC.

| Voltage<br>set points       | COMPARATOR                               |             | INTERFACE<br>STAGEI     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | INTERFACE<br>STAGE1 |                 | INTERFACE<br>STAGE1         |                            | NOT USED               |                 | ACTION                                                      |

|-----------------------------|------------------------------------------|-------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|-----------------------------|----------------------------|------------------------|-----------------|-------------------------------------------------------------|

|                             |                                          |             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                 |                             |                            |                        |                 |                                                             |

|                             |                                          |             | RB0                     | RBI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RB2                 | RB3             | RB4                         | RB5                        | RB6                    | RB7             | -                                                           |

| U1=14.4<br>Q5 on Q4<br>off  | UI                                       | PNP         | 1                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | losa                | 0               | <b>1</b> . <sub>1</sub>     | 0                          | 0                      | 0               | Disconnect array                                            |

|                             |                                          |             | inusia<br>Anno 1950 - D | 9.4<br>4.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4<br>1.4.4.4<br>1.4.4.4.4 |                     |                 |                             |                            |                        |                 |                                                             |

| L1=14<br>Q4 off<br>Q5 on    |                                          | NPN         | 0                       | 1.002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.15                | 0               | 1                           | 0                          | 0                      | 0               | Reconnect the charger with PWM                              |

|                             | mind state                               |             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                 | all<br>a                    | Chiefe State               |                        | naet<br>Juniti  | The design vi<br>the relay spect<br>freeh data site         |

|                             | 24 6406 24                               |             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                 |                             | in the                     | H.                     | talsa<br>n Isat | valtage of the<br>Reconstruction                            |

| U2=14.1<br>.Q3 on<br>Q2 off | ป2<br>22มาคา<br>สำ ระ<br>ประชา           | PNP         | 0                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                   | 0               | 1                           | 0                          | 0                      | 0               | PWM in charging state                                       |

|                             | 12-12/<br>(L-24 <u>L</u> ) <sup>22</sup> | and<br>Drie | ीः पूर्व                | L DOL L<br>SemiDo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                 |                             | 7                          | 12 Out                 | Si ac?          | it of <sub>0</sub> ¥ areniti<br>Notice vanta<br>Notice bins |

| L2≕13.8<br>Q3 on Q2<br>off  | OMR.IG.                                  | NPN         | 0                       | eko .<br>esiti-e<br>di mu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                   | 1               | 1                           | 0                          | 0                      | 0               | Continues charging                                          |

|                             | 2020.0                                   | 17. 21      | eft sir                 | wicti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                 |                             |                            |                        | 12,67.51        | Charger U                                                   |

| lor is<br>testice           |                                          |             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | tunte           | a Logié<br>1                | 200                        | 1.50                   | 12 23           | alt vilatini<br>arg a agniov                                |

| form<br>Incyn               |                                          |             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                 | est had                     |                            | The Lorent             | ghua            | soletarports Tre<br>ulti brioi schio                        |

| U3=12.8<br>Q1 on<br>Q0 off  | U3                                       | PNP         | 0                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                   | 11 1970         | an san<br>mis si<br>hal git | fair (**                   | $T \sim c^{2}$         |                 | charging state                                              |

| igni teli<br>Sgnaib         | - SPIC                                   |             |                         | 191<br>191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                   |                 |                             | s vois<br>of tail<br>origo |                        | asilov          | in charge cond<br>els the indutry<br>compositor 2           |

| inion) f                    | 10877091                                 | able        | Service U               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | 21. 12          |                             |                            | 16.04                  | nault           |                                                             |

| L3=11.7<br>Q1 off<br>Q0 on  | the de<br>No PIC.                        | NPN         | 0<br>boriup             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                   | 1<br>and<br>and | 0<br>alato<br>forts c       | oul Bu<br>nutro<br>A nu    | 0000<br>21. 22<br>1.20 | spinnte         | Disconnect the load                                         |

|                             |                                          |             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                 |                             |                            |                        |                 |                                                             |

1

Where;  $R_{Bo}$  to  $R_{BS}$  refer to the pick pines and  $Q_1$  to  $Q_8$  are the transistors in the interface stages. The above truth table represents the base for intelligent operation of the pick. Fig. 6 represents the flow chart of the proposed intelligent operation of the designed controller.

#### **Experimental Results**

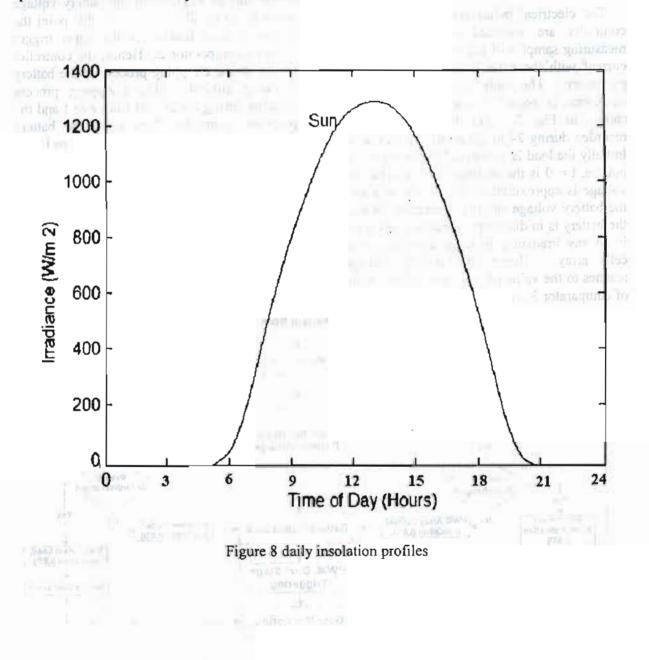

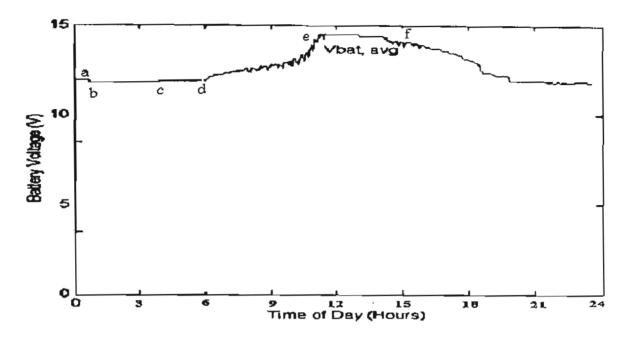

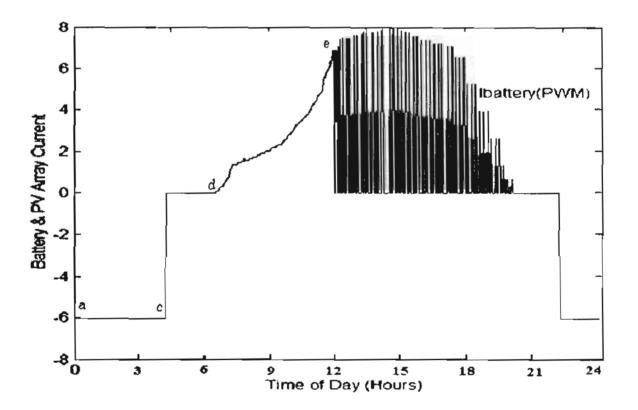

The electrical behaviors of the proposed controller are recorded experimentally by measuring samples of the battery voltage and current with the solar irradiance taken as a The daily profile of the solar parameter. irradiance is recorded during 24 hours as shown in Fig. 7. The battery voltage is recorded during 24 hours as shown in Fig. 8. Initially the load is connected to the battery at point a, t = 0 is the midnight, and the battery voltage is approximately 12 V. From a to c the battery voltage slightly decreases because the battery is in discharge condition and there is no any irradiance incident upon the solar Hence, the battery voltage cells array. reaches to the value of the lower trigger point of comparator 3 and the controller operates to disconnect the load. The last figure shows that the battery voltage at point c slightly This means that the controller increases. disconnects the load at this instant according to the proposed operating strategy. From c to d, the voltage of the battery remains constant because the load is disconnected during this period. From a to d, the charger, solar cells array, is connected with the battery. At point d, the sunrise begins and the battery voltage starts to go up till point e. At this point the battery voltage reaches to the upper trigger point of comparator 2. Hence, the controller begins in the chopping process of the battery charging current. The chopping process remains during the period from e to f and the proposed controller does allow the battery voltage to increase above U<sub>1</sub>, 14.4 V, as in the

Figure 7 Flow chart of proposed control scheme

#### E. 18 S. S. Eskander

proposed operation strategy. At point f, the load is connected again to the battery. Fig. 10 illustrates the daily profile of the battery charging current during 24 hours. Points a, c, d, e and f correspond to the same points in Fig. 9. The figure represents that at point c, the load is disconnected from the battery. At point d, the charging current increases till point e because the intensity of solar radiation increases during this period. The last figure clearly shows the chopping process during the period from e to f. At point f, the load is reconnected again to the battery.

The experimental results show the proper correspondence between the proposed operating strategy and the actual operation of the proposed system in actual field.

Figure 7 Plots offset of proposed control belieff.

Figure 9 Experimental measurement of battery voltage during 24 hours

Figure 10 Experimental measurement of charge current of the battery during 24 hours.

#### Conclusions

This paper presents the design of the intelligent charge-discharge controller for the energy storage element of a photovoltaic power system. The proposed controller is designed for protection purpose against overcharge and under discharge phenomena of the lead acid battery. The designed controller is suitable for any battery type because its design depends upon only the

#### E. 20 S. S. Eskander

voltage set points of the battery which are obtained experimentally or from the battery data sheet. The designed controller is an intelligent type because it is based on intelligent programmable chip. The proposed controller is very reliable because it operates according to definite programmable strategy. The operating strategy of the controller may be changed without any change in its design. Consequently, it has very high flexibility due to programmability. The proposed designed controller chops the battery charging current as the battery voltage reaches to certain definite value. The experimental results show the coincidence between the actual operation and the proposed operating strategy.

#### References

[1] Joseph R. Woodworth, Michael G. Thomas, John W. Stevens," EVALUATION OF THE BATTERIES AND CHARGE CONTROLLERS IN SMALL STAND-ALONE PHOTOVOLTAIC SYSTEMS ", 24th IEEE Photovoltaic Specialists Conference, 1994.

[2] John M. Hawkins," STORAGE DEVICES IN PV SYSTEM: LATEST DEVELOPMENTS, TECHNOLOGY AND INTEGRATION PROBLEMS", Solar Photovoltaic Energy Workshop '98, Telepower Australia Pty, Ltd, 1998.

[3] Tom Hund," BATTERY TESTING FOR PHOTOVOLTAIC APPLICATIONS", Photovoltaic System Application Department, Sandia National Laboratories, Albuquerque, January, 2004.

[4] Tom D. Hund,"PV HYBRID BATTERY TESTING", NREL, NCPV Program Review Meeting, 2000. [5] Thomas D. Hund, Bruce Thompson," AMP-HOUR COUNTING CHARGE CONTROL FOR PHOTOVOLTAIC HYBRID POWER SYSTEMS", 26th IEEE Photovoltaic Conference, Anaheim Sept. 1997.

[6] James P. Dunlop, P.E., "BATTERY AND CHARGE CONTROL IN STAND-ALONE PHOTOVOLTAIC SYSTEMS, FUNDAMENTAL AND APPLICATION", Sandia National Laboratories Report, Jan. 1997.

[7] Matthew A. Keyser, Ahmed Pesaran, Mark M. Mihalic," CHARGING ALOGORITHM FOR INCREASING LEAD ACID BATTERY CYCLE LIFE FOR ELECTRIC VEHICLES", 17th Electric Vehicle Symposium, Montreal, Canada, October, 16-18, 2000.

[8]D.Berndt," MAINTENANCE –FREE BATTERIES", Research Studies press LTD, 1993.

[9] Tomas Markvart," SOLAR ELECTRICITY "John Willy and Sons, 2000.

[10] J.Apllelbaum," STARTING AND STEADY STATE CHRACTERISTICS OF DC MOTOR POWERED BY SOLAR CELL GENERATORS", JEEE Transaction on energy conversions, march 1986.

W. Hemmann. W. Wiesner," [11]MODELLING OF PV MODULES-THE EFFECTS OF NON-UNIFORM IRRADIANCE ON PERFORMANCE MEASUREMENTS WITH SOLAR SIMULATORS". European 16th Photovoltaic Solar Energy Conference, Glawgow, UK, 1-5 May 2000.